Joulescope JS220 Recovery Request — Sensor FPGA Bricked During Update

Device Information

-

Model: JS220

-

Serial Number: 003415

-

Hardware Revision: 1

-

Original Firmware: FW 1.2.1 / FPGA 1.2.1

-

Target Update: FW 1.3.0 / FPGA 1.3.3

-

Joulescope UI Version: 1.4.1

-

Platform: macOS 26.4, Apple M1 Max (arm64)

Symptom

Solid blue LED. Device is detected on USB as “Joulescope JS220” (Jetperch LLC, serial 003415) but OP_CONNECT always times out. The Joulescope UI shows “driver open failed” on every launch.

What Happened

On 2026-04-07, a firmware update from FW 1.2.1/FPGA 1.2.1 → FW 1.3.0/FPGA 1.3.3 was initiated via the Joulescope UI (v1.4.1).

The update progressed through the updater state machine normally:

-

Updater1/updater2 version checks completed

-

Updater1 and updater2 were programmed successfully

-

Sensor FPGA (s/app1) erase completed successfully (mem_complete(0))

-

Sensor FPGA write started — approximately 50KB of 342KB was transferred via bulk OUT

-

USB pipe error —

libusb_submit_transfer returned -9(LIBUSB_ERROR_PIPE) -

Write timed out after 10 seconds

-

All subsequent erase retries returned

ABORTED(error code 24) -

The Joulescope UI was restarted (the progress bar was stuck at 0%)

After the restart, the device could never reconnect — OP_CONNECT times out on every attempt.

Recovery Attempts

CLI Recovery (pyjoulescope_driver 1.5.8)

Using raw mode (Driver.open(path, mode='raw')), we were able to:

-

Open the device successfully

Open the device successfully -

Erase and write

Erase and write h/mem/c/app(controller app v1.3.0) -

Erase and write

Erase and write h/mem/c/upd1(updater1 v1.2.1) -

Erase and write

Erase and write h/mem/c/upd2(updater2 v1.2.1) -

Reset to app mode — device re-enumerates as

Reset to app mode — device re-enumerates as u/js220/003415 -

Cannot erase or write

Cannot erase or write h/mem/s/app1— returnsPERMISSIONSerror from both updater1 and updater2 in raw mode

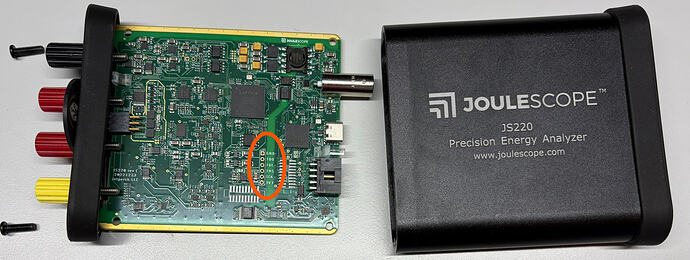

Root Cause Analysis

The sensor FPGA region (s/app1) requires a completed OP_CONNECT handshake to unlock memory write permissions. However, OP_CONNECT requires the FPGA to be functional to send the bulk IN connect response. Since the FPGA is erased/corrupt, this creates a deadlock:

-

OP_CONNECT → needs FPGA running → FPGA is blank

-

Write FPGA → needs OP_CONNECT → can’t connect

Raw mode bypasses the OP_CONNECT wait on the host side, but the device firmware still enforces the permission check.

Joulescope UI Attempt

After restoring the controller firmware, we launched the Joulescope UI (v1.4.1). Same result: OP_CONNECT timed out, driver open failed. The UI never reaches the device update dialog.

Current Device State

-

Controller app: v1.3.0 (freshly written, boots to app mode)

-

Updater1: v1.2.1 (freshly written)

-

Updater2: v1.2.1 (freshly written)

-

Sensor FPGA (s/app1): ERASED / PARTIALLY CORRUPT (original erase succeeded, write failed ~15% through)

-

USB enumeration: Device appears as “Joulescope JS220” with serial “003415”, idVendor=0x16D0, idProduct=0x10BA

Log Files

All log files are available at:

~/Library/Application Support/joulescope/log/

Key log files:

-

joulescope_20260407_235207_62612.log— Contains the original failed FPGA write attempt -

joulescope_20260407_234828_39715.log— Contains the initial update initiation -

joulescope_20260408_013056_15766.log— Latest UI attempt after CLI recovery of controller firmware

Request

Is there a way to recover this device? Possible approaches:

-

A firmware build or special tool that allows FPGA writes without requiring OP_CONNECT

-

JTAG/SWD recovery procedure

-

RMA/repair

Thank you for your help!